# Introduction to Programmable Logic Devices

John Coughlan RAL Technology Department Detector & Electronics Division

#### **PPD Lectures**

**Programmable Logic is Key Underlying Technology.**

- First-Level and High-Level Triggering

- Data Transport

- Computers interacting with Hardware (VME Bus)

- Silicon Trackers (Reading out Millions of Data Channels)

Commercial Devices. Developments driven by Industry. Telecomms, Gaming, Aerospace, Automotive, Set-top boxes....

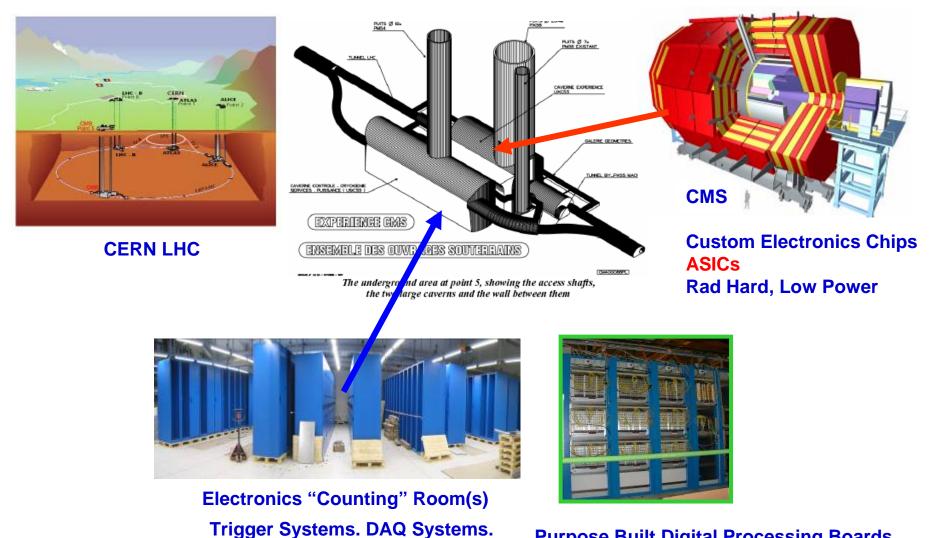

### **Particle Physics Electronics**

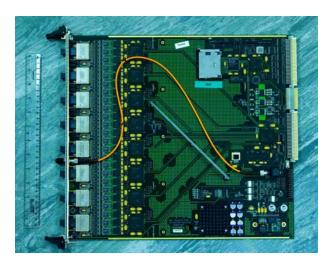

Purpose Built Digital Processing Boards In VME Bus Crates

## **Particle Physics Electronics**

- Special Dedicated Logic Functions (not possible in CPUs)

- Ultra Fast Trigger Systems (Trigger Algorithms) Clock Accurate Timing

- Massively Parallel Data Processing (Silicon Trackers with Millions of Channels)

**Custom Designed Printed Circuit Boards PCBs.**

**Commercial** Programmable Logic Devices

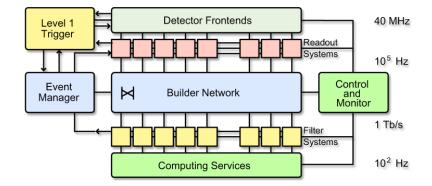

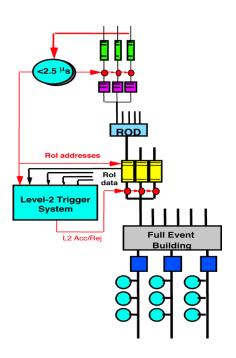

## CMS & ATLAS DAQ/Trigger Architectures

CMS

**ATLAS**

"Telecoms Network"

#### **Lecture Outline**

- Programmable Logic Devices

- Basics

- Evolution

- FPGA Field Programmable Gate Arrays

- Architecture

- Design Flow

- Design Tools

- Hardware Description Languages

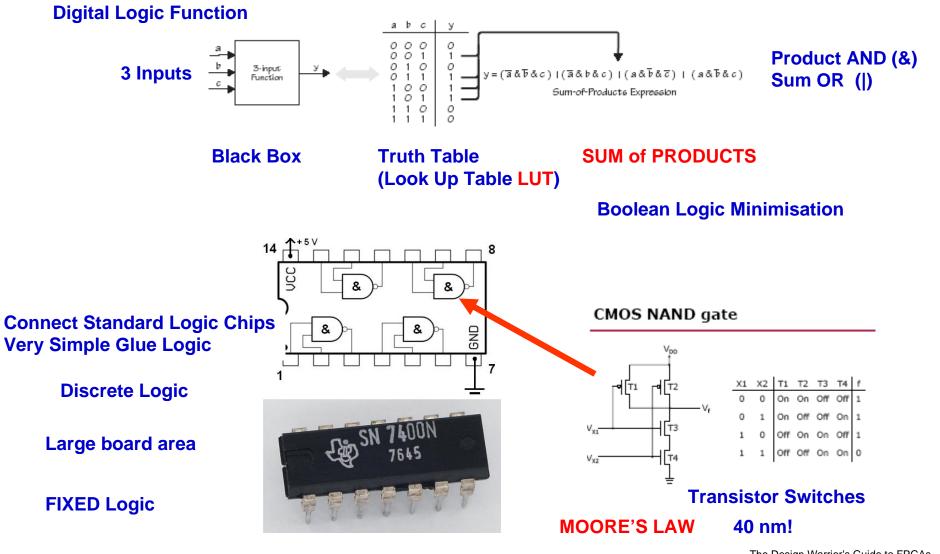

# **Digital Logic**

john.coughlan@stfc.ac.uk

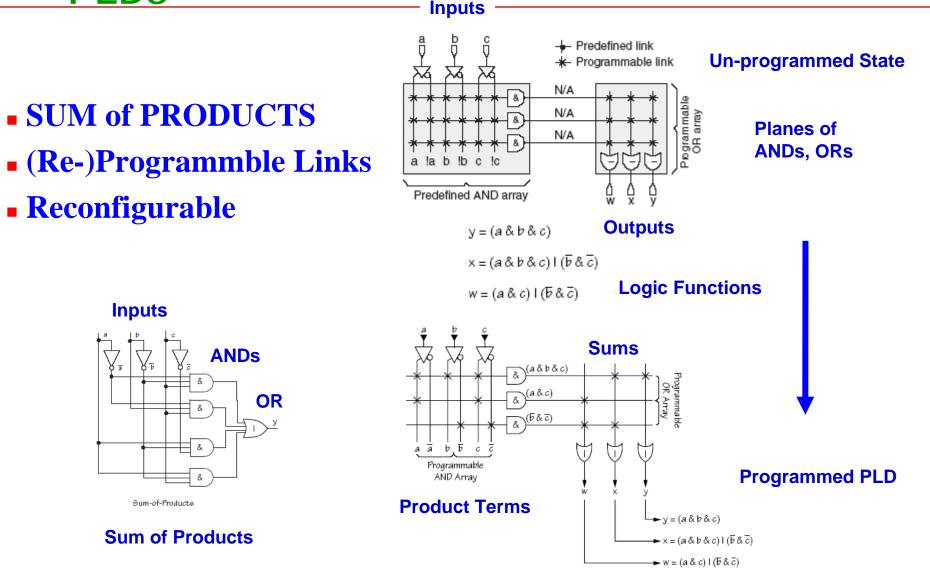

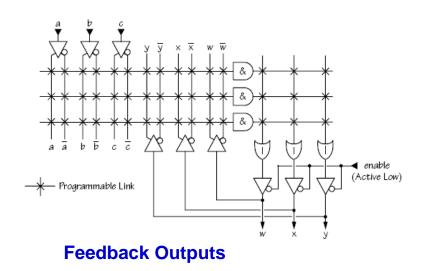

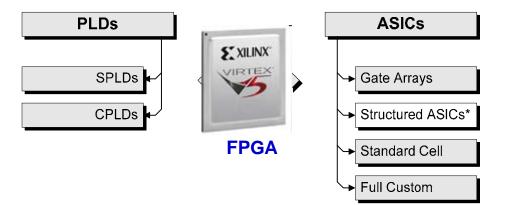

#### Programmable Logic Devices PLDs

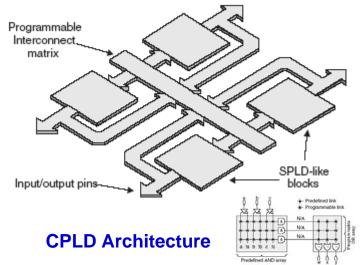

## **Complex PLDs**

- CPLDs

- Programmable PLD Blocks

- Programmable Interconnects

- Electrically Erasable links

#### Add Flip Flops/Registers (Clocked Logic) -> State Machines

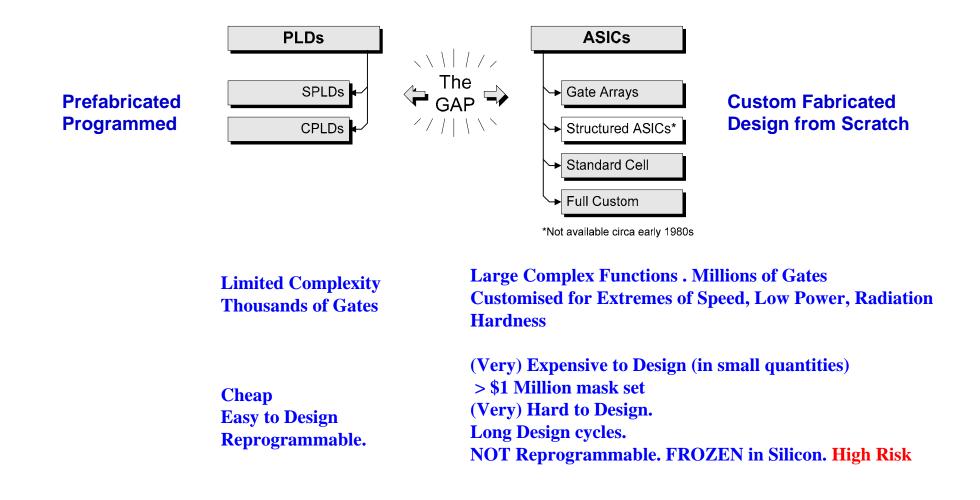

#### Application Specific Integrated Circuits ASICs

\*Not available circa early 1980s

#### **Large Complex Functions**

Inexpensive Easy to Design, Rapid Protoyping. Reprogrammable. Changing data standards.

> The Design Warrior's Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www.mentor.com)

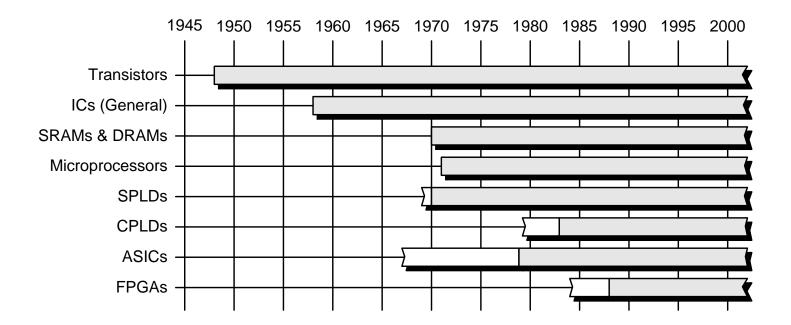

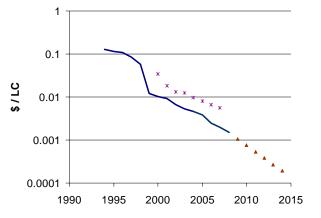

### Time line of Programmable devices

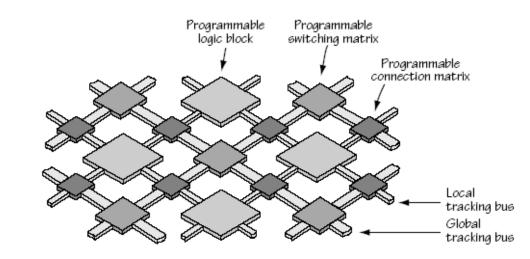

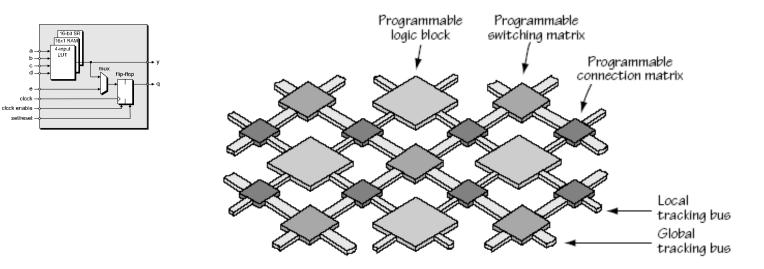

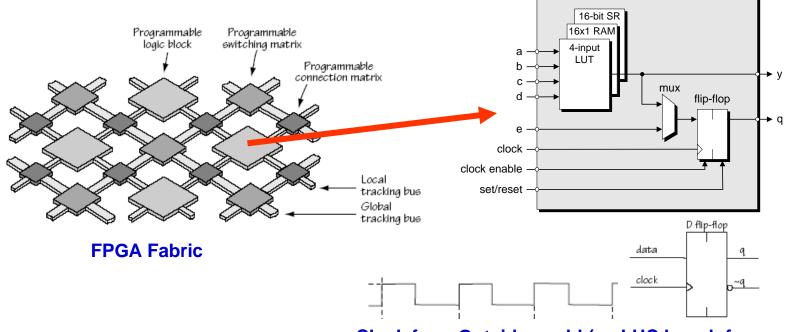

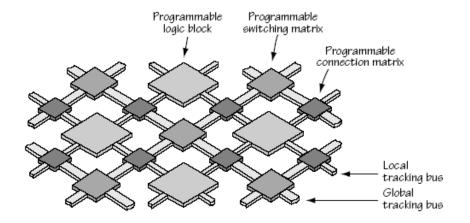

#### Field Programmable Gate Arrays FPGA

- Field Programmable Gate Array

- Simple' Programmable Logic Blocks

- Massive Fabric of Programmable Interconnects

- Standard CMOS Integrated Circuit fabrication process as for memory chips (Moore's Law)

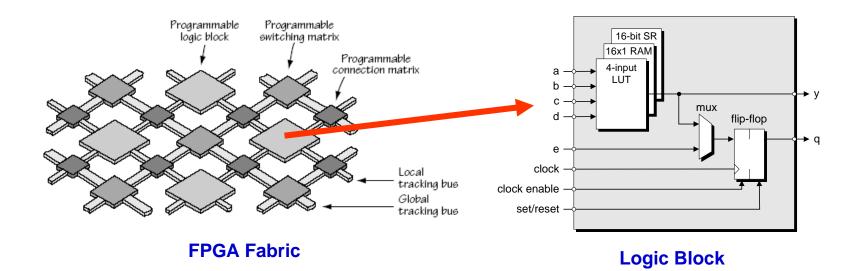

#### Huge Number of Logic Block 'Islands'

1,000 ... 100,000's +

in a 'Sea' of Interconnects

**FPGA** Architecture

The Design Warrior's Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www.mentor.com)

S. XILINX

/IRTEX

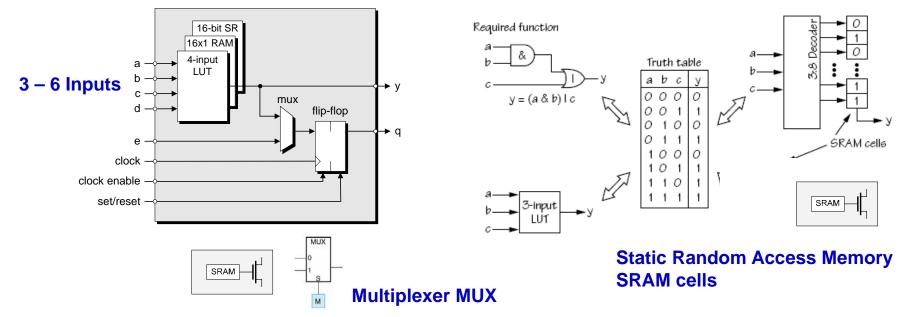

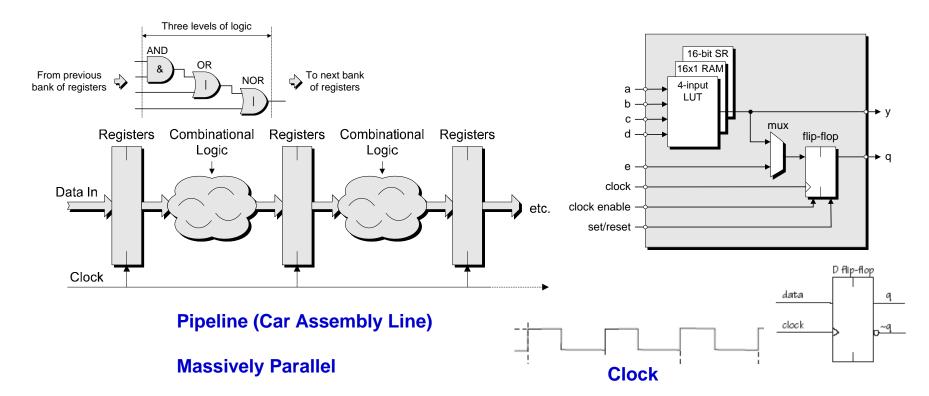

#### **Logic Blocks**

- Logic Functions implemented in Look Up Table LUTs. Truth Tables.

- Flip-Flops. Registers. Clocked Storage elements.

- Multiplexers (select 1 of N inputs)

## Look Up Tables LUTs

- LUT contains Memory Cells to implement small logic functions

- Each cell holds '0' or '1'.

- Programmed with outputs of Truth Table

- Inputs select content of one of the cells as output

#### 3 Inputs LUT -> 8 Memory Cells

The Design Warrior's Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www.mentor.com)

### **Logic Blocks**

Larger Logic Functions built up by connecting many Logic Blocks together

Fabric also has Larger Memory BlocksBlock SRAM useful for Data storageAnd other "Hard Wired" logic blocksEg CPUs, Memory Controllers...

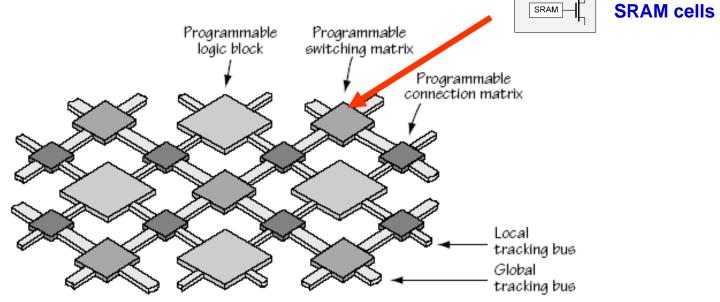

## **Programmable Routing**

- Connections Routing signals between Logic Blocks

- Determined by SRAM cells

**Special Routing for Clocks**

### **Clocked Logic**

- Registers on outputs. CLOCKED storage elements.

- Sequential Logic Functions (cf Combinational Logic LUTs)

- **Synchronous FPGA Logic Design, Pipelined Logic.**

- FPGA Fabric driven by Global Clock (e.g. LHC BX frequency)

#### **Clock from Outside world (eg LHC bunch frequency)**

### **Pipeline**

- Split the task into smaller steps with Registers in between.

- All driven by common clock

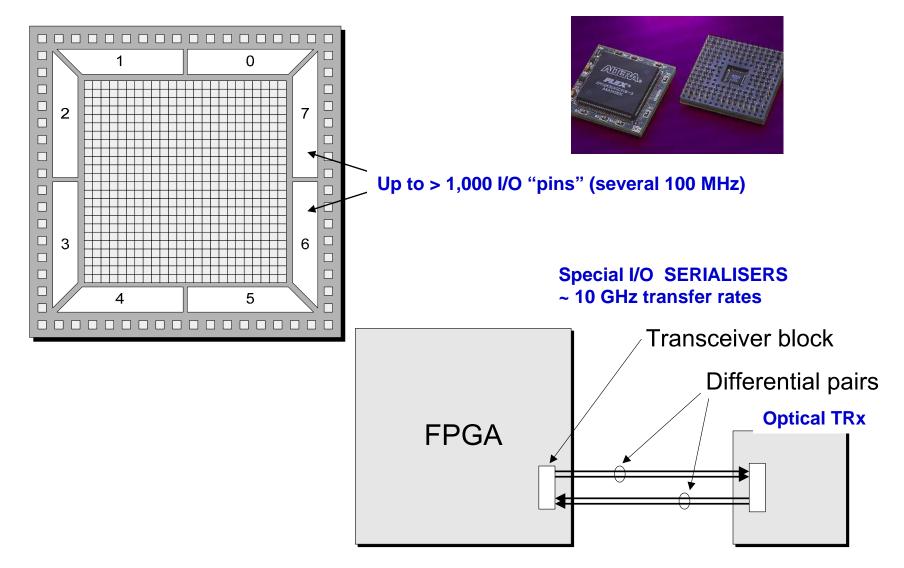

## Input Output I/O Getting data in and out

john.coughlan@stfc.ac.uk

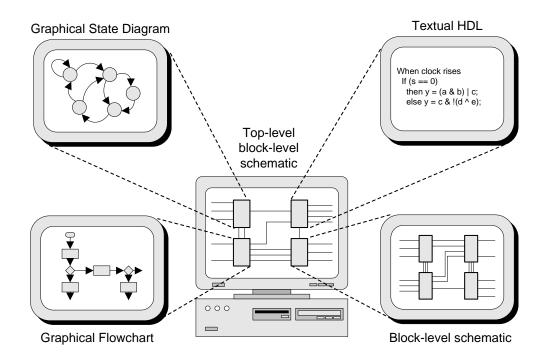

# **Designing Logic with FPGAs**

- Design Capture.

- High level Description of Logic Design.

- Graphical descriptions

- Hardware Description Language (Textual)

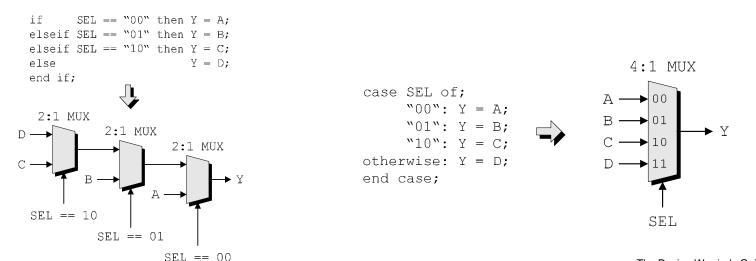

#### Hardware Description Languages

- Language describing hardware (Engineers call it FIRMWARE)

- Doesn't behave like "normal" programming language 'C/C++'

- Describe Logic as collection of Processes operating in Parallel

- Language Constructs for Multiplexers, FlipFlops ...etc

- Compiler (Synthesis) Tools recognise certain code constructs and generate appropriate logic

- Popular languages are VHDL, VERILOG

john.coughlan@stfc.ac.uk

#### **VHDL Firmware**

architecture Behavioral of dpmbufctrl is

Architecture / Logic Module

```

signal acount : std_logic_vector(31 downto 0);

signal dcount : std_logic_vector(31 downto 0);

signal bram_addr_i : std_logic_vector(31 downto 0);

```

begin

```

bram_en <='1';

bram_rst <= '0';</pre>

```

--bit order reverse address and data buses to match EDK scheme bram\_addr(0 to 31) <= bram\_addr\_i(31 downto 0);

Signals / Input Output to Module

#### Cf High Level Software Language C, C++

--N.B. EDK DOCM addresses are byte orientated count in 4s for whole words

```

Functions

Parallel Processes

g1 : process(clk, rst)

variable state : integer range 0 to 3;

Variables

variable buf zone: integer range 0 to 1;

Code Blocks

begin

Clocked Logic / Registers

if clk'event and clk = '1' then

if rst = '1' then

buf zone:=0;

acount <= (others => '0');

dcount <= (others => '0');

bram wen <= (others => '0');

Signal Assignments

bram addr i <= X"00001FFC"; --</pre>

bram dout i <= (others => '0');

state:=0;

elsif state = 0 then

--wait for din(0) at address 1FFC to be set to zero

--what about pipeline of BRAM - need to wait before polling?

bram wen <= (others => '0');

acount <= (others => '0');

bram addr i <= X"00001FFC";</pre>

bram dout i <= (others => '0');

dcount <= dcount;</pre>

if bram din i = X"00000000

state := 1;

If Else Blocks

Multiplexers

else

john.coughlan@stfc.ac.uk

state := 0;

end if;

```

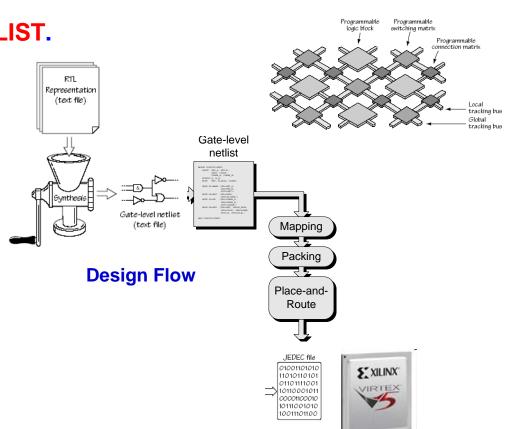

# **Designing Logic with FPGAs**

- High level Description of Logic Design

- Graphical descriptions

- Hardware Description Language (Textual)

- Compile (Synthesis) into NETLIST.

- Boolean Logic Gates.

- Target FPGA Device

- Mapping

- Routing

- Bit File for FPGA

- Commercial CAE Tools (Complex & Expensive)

- Logic Simulation

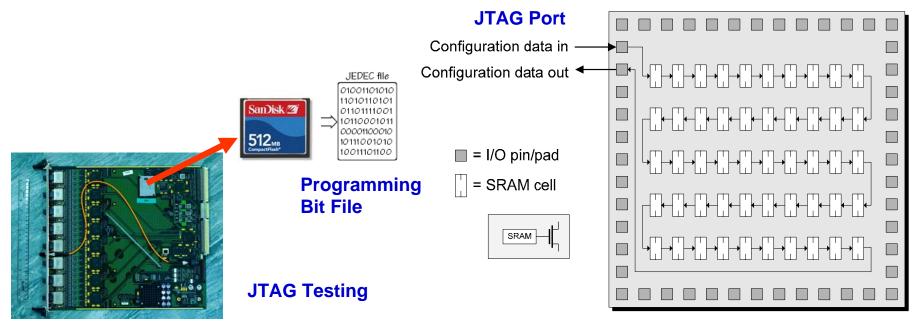

# **Configuring an FPGA**

- Millions of SRAM cells holding LUTs and Interconnect Routing

- Volatile Memory. Lose configuration when board power is turned off.

- Keep Bit Pattern describing the SRAM cells in non-Volatile Memory e.g. PROM or Digital Camera card

- Configuration takes ~ secs

#### Field Programmable Gate Arrays FPGA

- Large Complex Functions

- Re-Programmability, Flexibility.

- Massively Parallel Architecture

- Processing many channels simultaneously cf MicroProcessor sequential processing

- Fast Turnaround Designs ③

- Standard IC Manufacturing Processes (2)

- Leading Edge of Moore's Law ③

- Mass produced. Inexpensive. <sup>(3)</sup>

- Many variants. Sizes. Features. ©

- Not Radiation Hard ⊗

- Power Hungry ⊗

The Design Warrior's Guide to FPGAs Devices, Tools, and Flows. ISBN 0750676043 Copyright © 2004 Mentor Graphics Corp. (www.mentor.com)

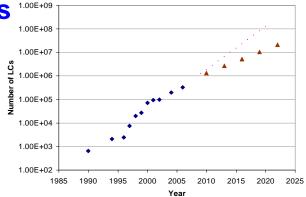

#### **FPGA** Trends

- State of Art is 40nm on 300 mm wafers

- Top of range >100,000 Logic Blocks

- >1,000 pins (Fine Pitched BGA)

- Problems

- Power. Leakage currents.

- Design Gap

- CAE Tools

### **Summary**

- Programmable Logic Devices

- Basics

- Evolution

- FPGA Field Programmable Gate Arrays

- Architecture

- Design Flow

- Hardware Description Languages

- Design Tools

**Importance for Particle Physics Experiments**